# Effects of Silicon Wafer's Resistivity on Passivation and Devices Performances of Solar Cell

Na Lin<sup>a</sup>, Shihua Huang b, \*

Provincial Key Laboratory of Solid State Optoelectronic Devices, Zhejiang Normal University, Jinhua Zhejiang, 321004, China

**Abstract:** In the manufacture of solar cells, the resistivity of silicon wafers has a crucial impact on their performance. This study investigated the effects of different resistivities on p-TOPCon solar cells. The results indicate that lower resistivity wafers have a higher implied open-circuit voltage ( $iV_{oc}$ ) value, but higher carrier mobility due to the low resistivity leads to an increase in saturation current density ( $J_0$ ). Conversely, solar cells made on higher resistivity silicon wafers have a lower carrier mobility, leading to slower electron-hole recombination and lower bulk recombination, resulting in the advantage of lower saturation current density and higher minority carrier lifetime. At the same time, simulation shows that as the resistivity increases, the  $V_{oc}$  and efficiency increase. However, cost considerations need to be taken into account as higher resistivity silicon wafers are more expensive. Therefore, resistivity between 2 - 3  $\Omega$ ·cm<sup>2</sup> is considered the preferred substrate for solar cells as it offers a better balance between cost and achieving high cell efficiency.

Keywords: TOPCon; Passivation; Resistivity.

#### 1. Introduction

Photovoltaic power generation has become one of the most cost-effective sources of renewable energy, and is expected to reach global grid parity within the next 3-5 years as its price continues to decrease. With its decreasing cost, photovoltaic power generation is poised to become one of the primary and most cost-effective sources of renewable energy, as well as a key driver of China's energy structure transformation.

Tunnel oxide passivated contact (TOPCon) solar cells technology has started to enter industrialization and is becoming a mainstream technology due to its advantages over other technologies.[1-3] With only a few core equipment additions, it can easily upgrade and replace passivated emitter and rear contact (PERC) production lines. The core structure of TOPCon technology includes ultra-thin oxide silicon and heavily doped poly-Si silicon film, which play important roles in passivation. The oxide silicon passivates dangling bonds on the surface of silicon wafers, inhibits minority carriers from entering the poly-Si silicon layer, and captures hydrogen atoms.[4,5] Meanwhile, heavily doped poly-Si and surface diffusion doping atoms reduce the concentration of minority carriers in the surface area.[6–8]Overall, TOPCon technology has great potential to further reduce the cost of photovoltaic power generation.

Solar cell efficiency and performance are influenced by numerous factors, and the resistivity of silicon wafers is a critical one[9]. During the manufacturing process, silicon wafers need to be doped with specific elements, usually boron or phosphorus, to achieve desired electrical properties. Generally, higher doping concentration results in lower resistivity of silicon wafers. The resistivity of silicon wafers affects the current flow and loss in solar cells, thus directly impacting their conversion efficiency.

Optimizing the resistivity of silicon wafers is, therefore, a crucial strategy to enhance solar cell efficiency. However, currently, the specific impact of silicon wafer resistivity remains unclear. This paper delves deeper into this subject

and reveals that a low resistivity yields a high implied opencircuit voltage  $(iV_{oc})$ , yet it also leads to an increase in saturation current density  $(J_0)$  and a decrease in minority carrier lifetime  $(\tau)$ . On the other hand, higher resistivity in silicon wafers reduces carrier mobility, leading to slower electron-hole recombination, lower bulk recombination, and a lower saturation current density, resulting in higher minority carrier lifetime. In solar cells, as the resistivity of the silicon wafer increases,  $V_{oc}$  and efficiency both gradually increase.

However, the purity of silicon wafers increases with higher resistivity, leading to higher production costs. Therefore, a balance must be achieved between wafer resistivity and passivation to increase solar cell efficiency while maintaining cost advantages.

## 2. Experiments

Passivation samples were prepared using planar p-type CZ c-Si wafers, which had a thickness of 165 µm and a resistivity (R) of  $0.8 - 6 \Omega \cdot \text{cm}$ . The wafers were first polished with an alkaline solution, followed by standard RCA cleaning. High concentration ozone gas (400 mg/L) was then generated and flowed into the diffusion furnace. After removing the asgrown oxide layer by immersing the wafers in 5 vol.% HF solution, they were subjected to oxidation at 400°C for 10 min. A 30 nm layer of boron-doped amorphous silicon was subsequently deposited on both sides of the ultra-thin SiO<sub>x</sub> coated wafers using an RF PECVD system. The crystallization of amorphous Si and activation of B dopant were performed by high temperature annealing at 800-1000°C for 30 minutes with N<sub>2</sub> atmosphere, followed by wet N<sub>2</sub> hydrogenation and aluminum oxide hydrogenation. The photo-conductance decay (PCD) can be measured by Sinton WCT-120 from which  $\tau_{\text{eff}}$ ,  $iV_{\text{oc}}$  and  $J_0$  for passivation quality characterization can be attained. The simulation was carried out using the free-version Quokka 2.5.

<sup>&</sup>lt;sup>a</sup> linna202208@163.com, <sup>b, \*</sup> huangshihua@zjnu.edu.cn

<sup>\*</sup> Corresponding author: Shihua Huang (Email: huangshihua@zjnu.edu.cn)

## 3. Results and Discussion

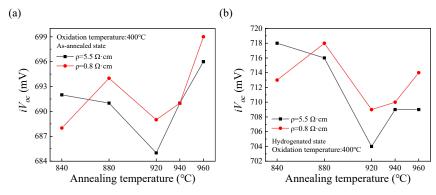

The  $iV_{\rm oc}$  is a critical parameter that serves as a key indicator of the efficiency and passivation quality of solar cells. The resistivity of silicon wafers plays a significant role in determining  $iV_{\rm oc}$ , as shown in Figure 1. Except for annealing

at 840°C, passivation samples made from low-resistivity silicon wafers (LW) exhibit considerably higher  $iV_{\rm oc}$  than those made from high-resistivity silicon wafers (HW), with a maximal increase of 5 mV. Notably, we also observed that HW samples exhibit a higher  $iV_{\rm oc}$  under low-temperature annealing, suggesting their superiority under such conditions.

**Figure 1.** (a-b)  $iV_{oc}$  of the as-annealed and AlO<sub>x</sub> hydrogenated p-TOPCon lifetime samples.

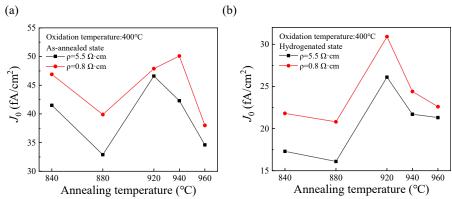

$J_0$  is a crucial indicator of passivation, and its value is also a key parameter to consider. As shown in Figure 2, it is evident that the  $J_0$  value for LW is higher than that for HW, indicating a negative impact of LW. This can be attributed to the fact that when the resistivity of the silicon wafer is high, electrons move more slowly in the silicon, and charges take longer to reach the electrode, thereby limiting the flow of

current. Therefore, HW will generate greater resistance to charge transport, resulting in a decrease in saturation current density. Conversely, when the resistivity of the silicon wafer is low, electrons move faster in the silicon and charges reach the electrode more quickly, resulting in faster current flow. As a result, LW generates less resistance to charge transport, leading to an increase in saturation current density.

Figure 2. (a-b)  $J_0$  of the as-annealed and AlO<sub>x</sub> hydrogenated p-TOPCon lifetime samples

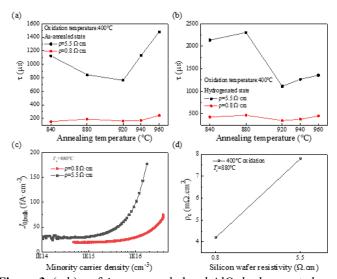

Similarly, the resistivity of a silicon wafer has a significant impact on minority carrier lifetime. As resistivity increases, the mobility of charge carriers decreases, causing a reduction in the rate of electron-hole recombination in solar cells. This leads to a decrease in bulk recombination and an increase in minority carrier lifetime. As shown in Figure 3(a, b), the  $\tau$  of HW is much higher than that of LW, with a maximum difference of 2000  $\mu$ s. Additionally, Figure 3(c) reveals that low silicon wafer resistivity helps to reduce  $J_{0,\text{bulk}}$  from 30.6 to 19.5 fA/cm<sup>2</sup> ( $\Delta n = 1 \times 10^{15}$  cm<sup>-3</sup>). The corresponding contacts, shown in Figure 3(d), satisfy the requirements for solar cell fabrication.

Equation (1) is the formula for calculating resistivity. It can be seen that resistivity is affected by both carrier concentration and mobility. At low resistivity, the doping concentration is higher and recombination is more likely to occur.

$$\rho = \frac{1}{pq\mu_p} \tag{1}$$

$\rho$  is silicon wafer resistivity, p is carrier concentration in p-type silicon wafers, q is the charge, and  $\mu_p$  is the mobility of charge carriers in p-type silicon wafers.

**Figure 3.** (a-b)  $\tau$  of the as-annealed and AlO<sub>x</sub> hydrogenated p-TOPCon lifetime samples. (c) The  $J_{0,\text{bulk}}$  after hydrogenated, annealed at  $T_a$ =880°C. (d) Contact resistivity measured by TLM method, annealed at  $T_a$  = 880°C.

**Table 1.**  $N_A$  and  $\tau_{\text{intrinsic}}$  of different wafer resistivity

| Wafer Resistivity (Ω·cm) | $N_{ m A}({ m cm}^{-3})$ | $	au_{ m intrinsic} \left( \mu { m s}  ight)$ |

|--------------------------|--------------------------|-----------------------------------------------|

| 0.8                      | 1.93612E+16              | 448.6                                         |

| 5.5                      | 2.50372E+15              | 3924.7                                        |

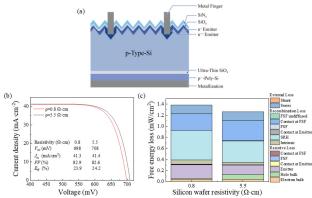

Finally, we simulated the performance of p-TOPCon solar cells using Quokka 2.5 and predicted the results for HW and LW. The simulation results are presented in Figure 4, with the corresponding parameters listed in Table 2. Furthermore, Table 1 illustrates the relationship between silicon wafer resistivity and lifetime. By solely altering the resistivity of the silicon wafer, it can be observed that  $V_{\rm oc}$  increases with the increase of the resistivity of the silicon wafer, which is

inconsistent with the trend of  $iV_{\rm oc}$ . The reason for this inconsistency is that the recombination loss of metal and silicon is not considered under the sinton test. It can be noticed that increasing wafer resistivity helps to reduce the intrinsic and SRH recombination losses, as shown in Figure 4 (c).

Table 2. Parameter for simulations

| structure                                    | TOPCon                                                     |

|----------------------------------------------|------------------------------------------------------------|

| Cell thickness                               | 165 μm                                                     |

| p-type bulk resistivity                      | Variable                                                   |

| Bulk lifetime                                | Variable                                                   |

| Auger model                                  | Richter 2012                                               |

| Generation current                           | 43.12                                                      |

| Series resistance                            | 0.1 mΩ·cm <sup>2</sup>                                     |

| Shunt resistance                             | 1×10 <sup>5</sup> Ω·cm <sup>2</sup>                        |

| Front Side:                                  |                                                            |

| Front contact shape                          | Line, width 20μm                                           |

| Finger space                                 | 600 μm                                                     |

| Junction depth, n <sup>++</sup>              | 500 nm                                                     |

| Front $J_{0,met}$                            | 20 fA/cm <sup>2</sup>                                      |

| Front R <sub>sheet, n++</sub>                | 90 Ω/sq                                                    |

| Front width of n <sup>++</sup>               | 20 μm                                                      |

| Front $J_{\theta, n++}$                      | 20 fA/cm <sup>2</sup>                                      |

| Junction depth, n <sup>+</sup>               | 200 nm                                                     |

| Front $J_{0,pass}$                           | 20 fA/cm <sup>2</sup>                                      |

| Front R <sub>sheet, n+</sub>                 | 140 Ω/sq                                                   |

| Front contact resistivity                    | 0.1 mΩ·cm <sup>2</sup>                                     |

| Rear Side:                                   |                                                            |

| Rear contact shape                           | Full                                                       |

| Finger space                                 | 600 μm                                                     |

| Junction depth, p <sup>+</sup>               | 300 nm                                                     |

| Rear R <sub>sheet, p+</sub>                  | 30 Ω/sq                                                    |

| Rear $J_0$                                   | 5 fA/cm <sup>2</sup>                                       |

| Rear $J_{0,met}$<br>Rear contact resistivity | $10 \text{ fA/cm}^2$ $1 \text{ m}\Omega \cdot \text{cm}^2$ |

| Optical model:                               | 1 11152 C111                                               |

| Passivation & Reflectance                    | SiO <sub>2</sub> 2 nm                                      |

| Layer ( $SiN_x$ , $n=2$ )                    | SiN <sub>x</sub> 73 nm                                     |

| Shading width of finger                      | 100%                                                       |

| $Z_0$                                        | 6                                                          |

**Figure 4.** (a) The simulated light *I–V* curves of resistivity of different silicon wafers. (b) The simulated light *I–V* curves and (c) the free energy loss analysis (FELA) of different silicon wafers resistivity

## 4. Conclusion

Silicon wafers are the foundation for manufacturing solar cells. This study investigates the impact of different resistivities of silicon wafers on the passivation and efficiency of p-type TOPCon solar cells. The result reveals that lowresistivity wafers have the advantage of a high  $iV_{oc}$ , but also exhibit an increase in saturation current density due to faster carrier mobility. As the resistivity of the silicon wafer increases, carrier mobility decreases, leading to slower recombination rates and a decrease in saturation current density. This makes high-resistivity wafers favorable due to their low saturation current density and high carrier lifetime. At the same time, it is shown by simulation that as the resistivity increases, the  $V_{\rm oc}$  increases and the efficiency increases. It should be noted that higher resistivity wafers are more expensive. Ultimately, a resistivity range of 2 - 3  $\Omega \cdot \text{cm}^2$ is recommended as the optimal substrate for solar cells.

# Acknowledgments

This work was supported by the Key Research and Development Program of Zhejiang Province (2021C01006).

#### References

- [1] S.W. Glunz, B. Steinhauser, J.I. Polzin, C. Luderer, B. Grübel, T. Niewelt, A.M.O.M. Okasha, M. Bories, H. Nagel, K. Krieg, F. Feldmann, A. Richter, M. Bivour, M. Hermle, Silicon-based passivating contacts: The TOPCon route, Progress in Photovoltaics: Research and Applications. (2021).

- [2] J. Schmidt, R. Peibst, R. Brendel, Surface passivation of crystalline silicon solar cells: Present and future, Solar Energy Materials and Solar Cells. 187 (2018) 39–54.

- [3] F. Feldmann, M. Simon, M. Bivour, C. Reichel, M. Hermle, S.W. Glunz, Carrier-selective contacts for Si solar cells, Appl Phys Lett. 104 (2014).

- [4] Y. Huang, M. Liao, Z. Wang, X. Guo, C. Jiang, Q. Yang, Z. Yuan, D. Huang, J. Yang, X. Zhang, Q. Wang, H. Jin, M. Al-Jassim, C. Shou, Y. Zeng, B. Yan, J. Ye, Ultrathin silicon oxide prepared by in-line plasma-assisted N2O oxidation (PANO) and the application for n-type polysilicon passivated contact, Solar Energy Materials and Solar Cells. 208 (2020).

- [5] Y. Zeng, H. Tong, C. Quan, L. Cai, Z. Yang, K. Chen, Z. Yuan, C.H. Wu, B. Yan, P. Gao, J. Ye, Theoretical exploration towards high-efficiency tunnel oxide passivated carrierselective contacts (TOPCon) solar cells, Solar Energy. 155 (2017) 654–660.

- [6] T.F. Wietler, D. Tetzlaff, J. Krügener, M. Rienäcker, F. Haase, Y. Larionova, R. Brendel, R. Peibst, Pinhole density and contact resistivity of carrier selective junctions with polycrystalline silicon on oxide, Appl Phys Lett. 110 (2017).

- [7] D. Yan, A. Cuevas, J.I. Michel, C. Zhang, Y. Wan, X. Zhang, J. Bullock, Polysilicon passivated junctions: The next technology for silicon solar cells?, Joule. 5 (2021) 811–828.

- [8] M. Singh, R. Santbergen, L. Mazzarella, A. Madrampazakis, G. Yang, R. Vismara, Z. Remes, A. Weeber, M. Zeman, O. Isabella, Optical characterization of poly-SiOx and poly-SiCx carrier-selective passivating contacts, Solar Energy Materials and Solar Cells. 210 (2020).

- [9] A. Richter, J. Benick, F. Feldmann, A. Fell, M. Hermle, S.W. Glunz, n-Type Si solar cells with passivating electron contact: Identifying sources for efficiency limitations by wafer thickness and resistivity variation, Solar Energy Materials and Solar Cells. 173 (2017) 96–105.